NAND-poort: verschil tussen versies

nodig |

|||

| Regel 1: | Regel 1: | ||

De '''NAND-poort''' (''Nederlands: '''NEN-poort''''') is een [[digitaal|digitale]] [[elektronica|elektronische schakeling]]. De poort bezit twee of meer ingangen en één uitgang. De logische toestand van de uitgang is uitsluitend 0, als alle ingangen 1 zijn. De NAND-poort is in een transistor-schakelschema het basiscircuit voor alle overige logische poorten (NOT, AND, OR, NOR, XOR, etc.). Met NOR kan het ook, maar voor een NAND zijn maar twee [[transistor]]s nodig. |

De '''NAND-poort''' (''Nederlands: '''NEN-poort''''') is een [[digitaal|digitale]] [[elektronica|elektronische schakeling]]. De poort bezit twee of meer ingangen en één uitgang. De logische toestand van de uitgang is uitsluitend 0, als alle ingangen 1 zijn. De NAND-poort is in een transistor-schakelschema het basiscircuit voor alle overige logische poorten (NOT, AND, OR, NOR, XOR, etc.). Met NOR kan het ook, maar voor een NAND zijn maar twee [[transistor]]s nodig. |

||

==Overdrachtsfunctie== |

|||

==[[Booleaanse algebra|Booleaanse]] overdrachtsfunctie== |

|||

De [[Booleaanse algebra|booleaanse]] overdrachtsfunctie <math>Q</math> van een NAND-poort met ingangen <math>P_1,\ldots, P_n</math> is |

|||

<math>Q=\overline{\prod_{i=1}^ |

:<math>Q = \overline{\prod_{i=1}^n P_i} =\overline{P_1 \cdot P_2 \cdot \ldots\cdot P_n}</math> |

||

Volgens de [[wetten van De Morgan]] |

Volgens de [[wetten van De Morgan]] kan dit ook geschreven worden als: |

||

<math>Q=\sum_{i=1}^ |

:<math>Q = \sum_{i=1}^n \overline{P_i} = \overline{P_1} + \overline{P_2} + \ldots + \overline{P_n}</math> |

||

==Waarheidstabel voor een poort met 2 ingangen== |

==Waarheidstabel voor een poort met 2 ingangen== |

||

Versie van 24 nov 2020 23:26

De NAND-poort (Nederlands: NEN-poort) is een digitale elektronische schakeling. De poort bezit twee of meer ingangen en één uitgang. De logische toestand van de uitgang is uitsluitend 0, als alle ingangen 1 zijn. De NAND-poort is in een transistor-schakelschema het basiscircuit voor alle overige logische poorten (NOT, AND, OR, NOR, XOR, etc.). Met NOR kan het ook, maar voor een NAND zijn maar twee transistors nodig.

Overdrachtsfunctie

De booleaanse overdrachtsfunctie van een NAND-poort met ingangen is

Volgens de wetten van De Morgan kan dit ook geschreven worden als:

Waarheidstabel voor een poort met 2 ingangen

| Ingangen | Uitgang | |

|---|---|---|

| P1 | P2 | Q |

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

Waarheidstabel voor een poort met 3 ingangen

| Ingangen | Uitgang | ||

|---|---|---|---|

| P1 | P2 | P3 | Q |

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 |

Elektronische implementatie

NAND-poorten worden, meestal in groepen of in combinatie met andere logische schakelingen, als geïntegreerde schakeling uitgevoerd. Meestal is het positieve logica; een logische 1 correspondeert met een hoge spanning. Het type 7400 uit de TTL-serie 74xx is een voorbeeld van een viervoudige NAND met elk twee ingangen.

Uitvoering

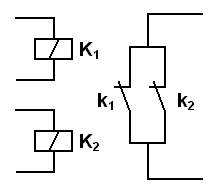

Uitvoering met relais

In de schakeling met relais bezit elk relais een verbreekcontact. De stroomkring met de contacten is slechts geopend, wanneer alle relais bekrachtigd zijn. Positieve logica: 1 = stroomvoerend

Uitvoering met transistoren

Indien beide ingangen onder spanning staan, laten beide transistoren stroom door en wordt de uitgang geaard. Indien echter een van beide ingangen niet onder spanning staat, laat een van beide transistoren geen stroom door en ontstaat een uitgangsspanning.

Etymologie

Het woord NAND bestaat niet in de Engelse taal. Het kan worden gezien als een samentrekking van NOT en AND. Het kan ook worden gezien als een woord dat gemaakt is naar analogie van NOR, dat wél een goed Engels woord is.